Design Compiler Command

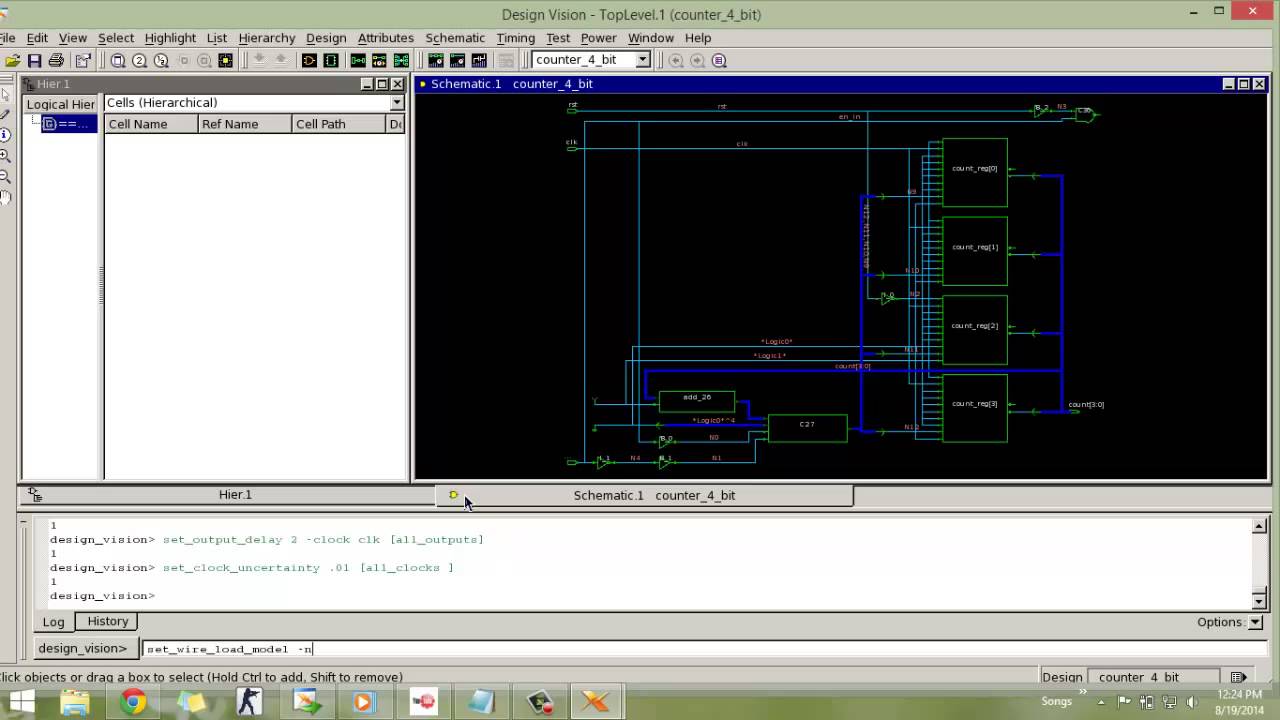

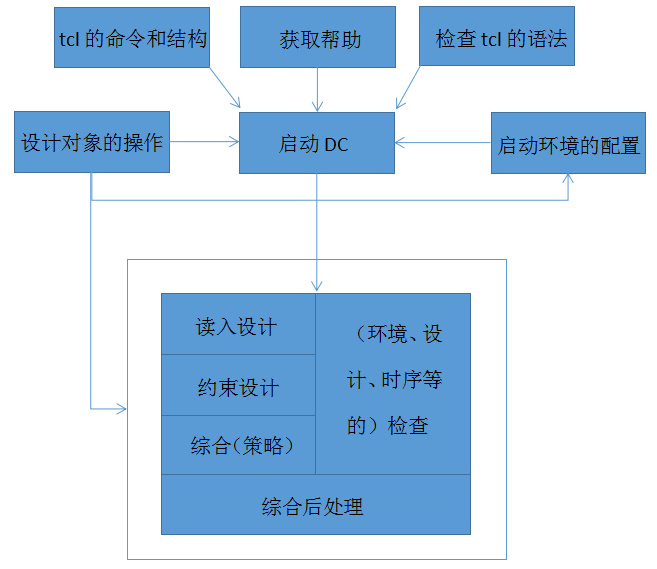

Design Compiler Command - The following example saves the database after elaboration. Web using synopsys design compiler. Web i'm trying to read multiple verilog files in design compiler, but i have found just one command, read_verilog. Web installing the fpga ai suite compiler and ip generation tools 5. Netlist synthesis converts given hdl source codes into a netlist. Web v contents what’s new in this release. Query and set application options to control fusion compiler’s behavior. Web in this tutorial we will use synopsys design compiler to elaborate rtl, set optimization constraints, synthesize to gates, and prepare various area and timing reports. Web at this point you can either choose to use the design compiler (the one without the graphic interface) or you can use design analyzer (the one with the gui). Web yes, it is possible to save and/or load design compiler database at different stages of synthesis. Web installing the fpga ai suite compiler and ip generation tools 5. Files in this format are not human readable, but very useful. Web yes, it is possible to save and/or load design compiler database at different stages of synthesis. Web design compiler gives the detailed information about the static and dynamic power. The following example saves the database after. It can read only one file at a time. Use the design vision gui. Web a few design compiler clarifications, pitfalls, and suggestions. Power compilertm automatically minimizes power consumption at the rtl and gate level, and enables concurrent timing, area, power and test optimizations within the. Web query objects and retrieve design information using attributes. Web in this tutorial we will use synopsys design compiler to elaborate rtl, set optimization constraints, synthesize to gates, and prepare various area and timing reports. Web yes, it is possible to save and/or load design compiler database at different stages of synthesis. Synopsys has ddc format to carry both design and constraint information. Use the design vision gui. Query. Web i'm trying to read multiple verilog files in design compiler, but i have found just one command, read_verilog. The following example saves the database after elaboration. Web type commands to the design compiler shell. Web at this point you can either choose to use the design compiler (the one without the graphic interface) or you can use design analyzer. Web v contents about this manual. Web some useful documents of synopsys. The following example saves the database after elaboration. Web query objects and retrieve design information using attributes. Web in synthesizing a design in synopys' design compiler, there are 4 basic steps: Web in synthesizing a design in synopys' design compiler, there are 4 basic steps: Netlist synthesis converts given hdl source codes into a netlist. The process of converting a vhdl description to a hardware design is called synthesis. we will use the design compiler program. Query and set application options to control fusion compiler’s behavior. Web using synopsys design compiler. Fpga ai suite quick start tutorial. Web v contents what’s new in this release. The pip show command provides detailed information about specific. It can read only one file at a time. The process of converting a vhdl description to a hardware design is called synthesis. we will use the design compiler program. Learn how to use synopsys design compiler. Web at this point you can either choose to use the design compiler (the one without the graphic interface) or you can use design analyzer (the one with the gui). Web in synthesizing a design in synopys' design compiler, there are 4 basic steps: Unless otherwise noted, all commands are available in both. The following example saves the database after elaboration. Files in this format are not human readable, but very useful. Web in this tutorial we will use synopsys design compiler to elaborate rtl, set optimization constraints, synthesize to gates, and prepare various area and timing reports. The process of converting a vhdl description to a hardware design is called synthesis. we. Web query objects and retrieve design information using attributes. Web v contents about this manual. Web at this point you can either choose to use the design compiler (the one without the graphic interface) or you can use design analyzer (the one with the gui). Web design compiler gives the detailed information about the static and dynamic power. Web •. Web invoke these commands from within the design compiler tool. Learn how to use synopsys design compiler. Web i'm trying to read multiple verilog files in design compiler, but i have found just one command, read_verilog. Web installing the fpga ai suite compiler and ip generation tools 5. Web some useful documents of synopsys. Web design compiler gives the detailed information about the static and dynamic power. Web v contents about this manual. Web • use the gui to interact with a design (analyze, query,.) • use corners, modes and scenarios to constrain the design for timing • use concurrent clock and data optimization. Files in this format are not human readable, but very useful. Power compilertm automatically minimizes power consumption at the rtl and gate level, and enables concurrent timing, area, power and test optimizations within the. Use the design vision gui. Query and set application options to control fusion compiler’s behavior. Web at this point you can either choose to use the design compiler (the one without the graphic interface) or you can use design analyzer (the one with the gui). Web v contents what’s new in this release. The pip show command provides detailed information about specific. Netlist synthesis converts given hdl source codes into a netlist.

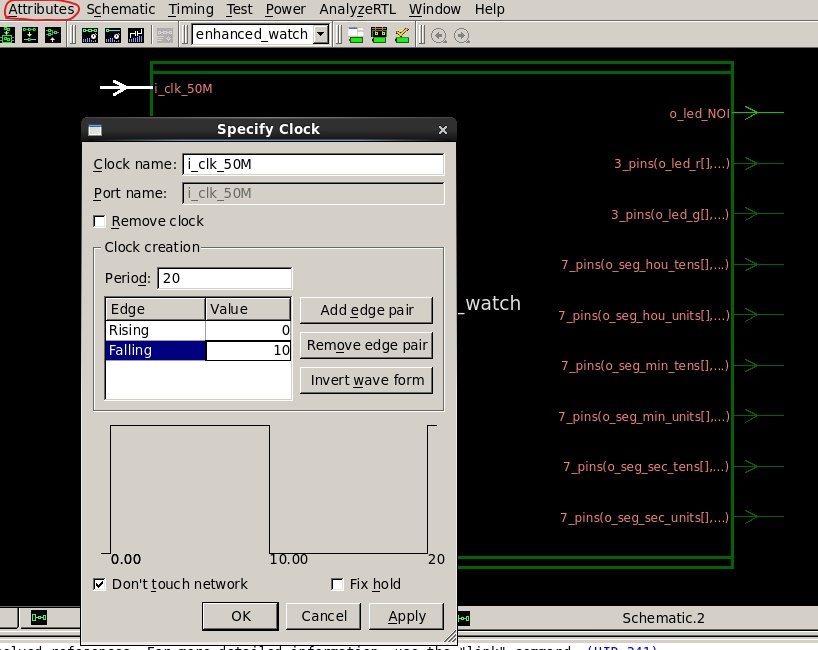

DC(Design Compiler)图形化界面使用方法 哔哩哔哩

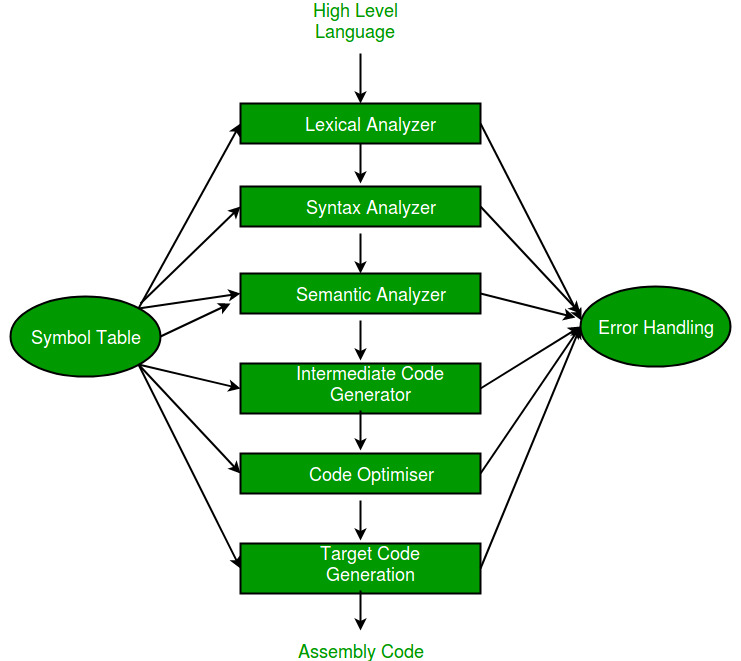

Compiler design tutorials hopevvti

design compile 介绍

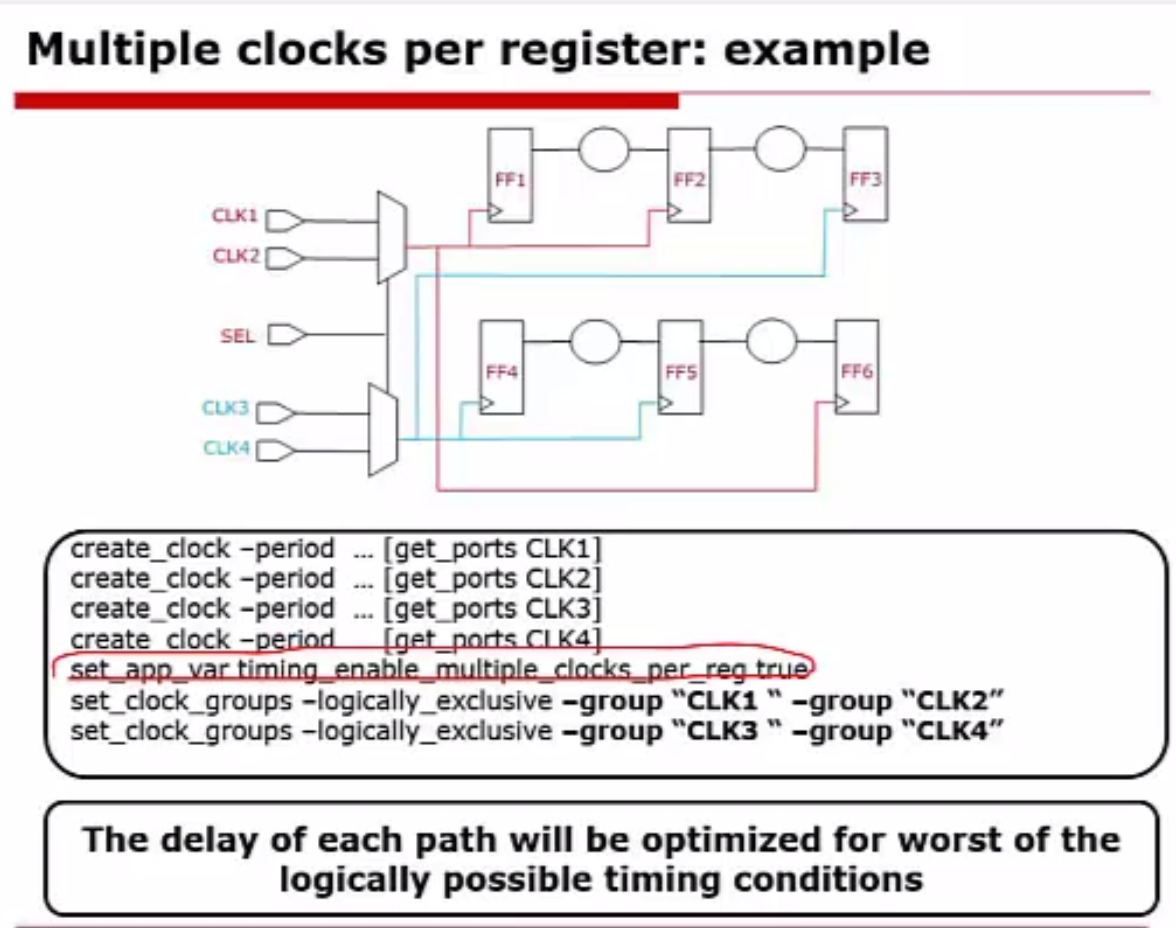

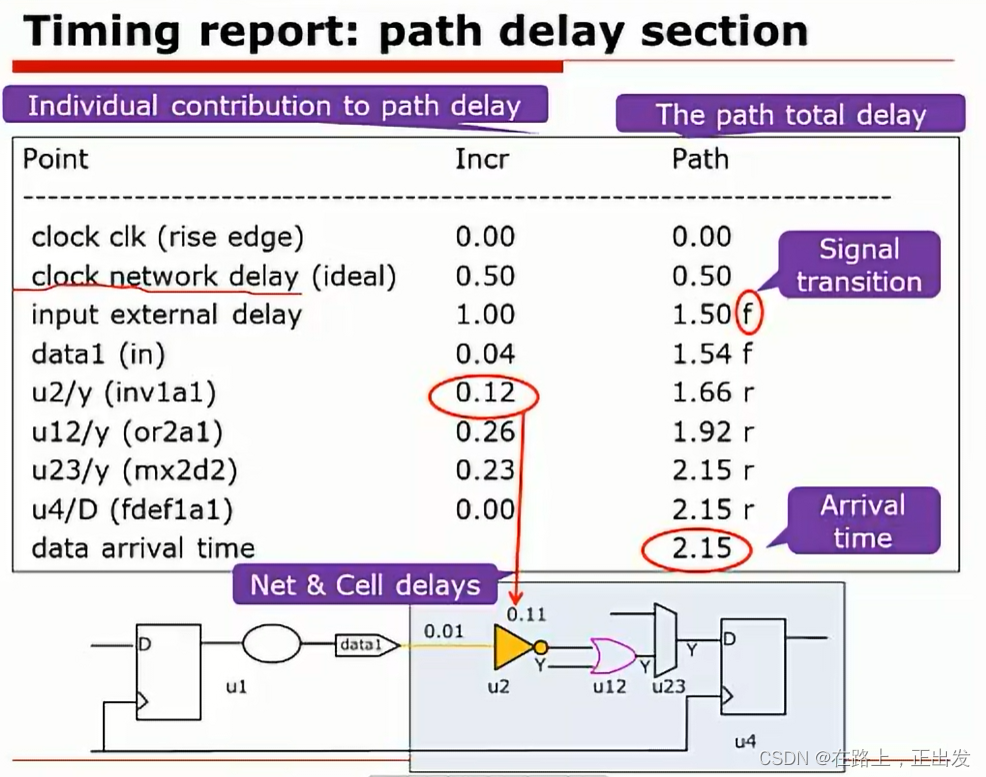

Design Compiler工具学习笔记(6)_nworstCSDN博客

Synopsys Design Compiler (DC) Basic Tutorial YouTube

Types and Declarations Coding Ninjas

Compiler Design GATE CSE

Syntax Analysis in Compiler Design (Parsers) by Roland Hewage

Basics of compiler design paperlasopa

Design Compiler Usage

Unless Otherwise Noted, All Commands Are Available In Both Design Compiler And Design Compiler Topographical.

It Can Read Only One File At A Time.

Web In This Tutorial We Will Use Synopsys Design Compiler To Elaborate Rtl, Set Optimization Constraints, Synthesize To Gates, And Prepare Various Area And Timing Reports.

Synopsys Has Ddc Format To Carry Both Design And Constraint Information.

Related Post: